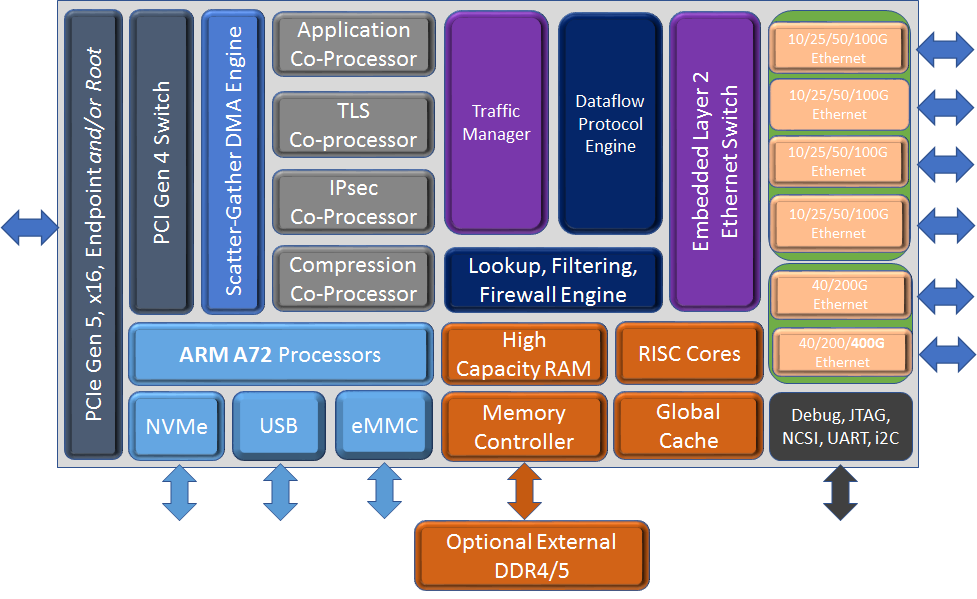

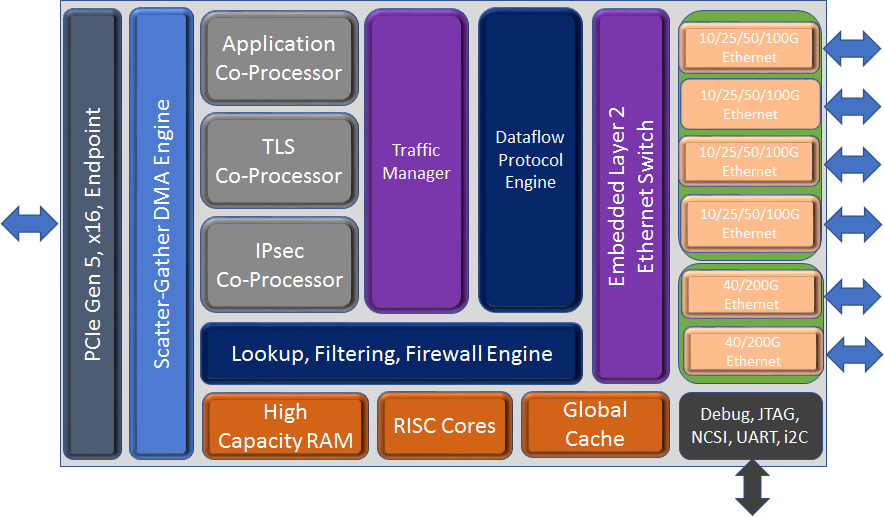

Chelsio’s T7 is a quad port 1/10/25/50/100Gb, dual port 40/100/200Gb, or single port 400Gb Ethernet Unified Wire DPU ASIC with a PCI Express 5.0 host bus interface, optimized for storage, cloud computing, HPC, virtualization and other datacenter networking applications.

The seventh generation T7 ASIC technology from Chelsio provides the highest performance and efficiency, with dramatically lower host-system CPU communications overhead thanks to on-board hardware that offloads TCP/IP, UDP/IP, iSCSI, FCoE, Unified RDMA (RoCEv2 & iWARP), TLS/IPsec, NVMe-oF, and NVMe/TCP processing from its host system and frees up host CPU cycles for user applications. As a result, the system benefits from higher bandwidth, lower latency, and reduced power consumption.

T7 runs the predecessor T4, T5, & T6 silicon software without modification so as to enable leveraging of the user’s existing software investment.

T7’s architecture is Chelsio’s 7th generation DPU technology road-tested across several tier-1 OEMs over the years and has evolved to support all offloads using either card memory or host memory. As a result, T7 technology can now enable a full featured DPU technology in a small memory-free package to address server and cloud applications at an aggressive price point.

The Smart NIC Programmable DPU Solution

In addition to the above offloads, versions of T7 integrate 8 A72 Arm cores that are exposed to the user. These Arm cores offload the traffic to the integrated 400Gb DPU on the chip and as a result the Arm cores are available to support the user’s specific application. The T7 transport engine is a programmable DPU that can offload protocol processing per connection, per-server, per-interface, while simultaneously providing complete stateless offload to traffic for non-offloaded connections (processed by operating systems stack running on host CPU). The T7 also provides a flexible direct data placement capability for regular TCP sockets, with all the benefits of zero-copy and kernel bypass without rewriting the applications. To support the Arm Cores, Chelsio provides a full development and debug software package to allow development of application specific firmware.

T7 is available in different variants. For list of features supported with each variant, ordering information and Applications, please refer the Product Briefs in Related Links.

Related Links: